Page 35 - Template EBook Kita (A4 Document)

P. 35

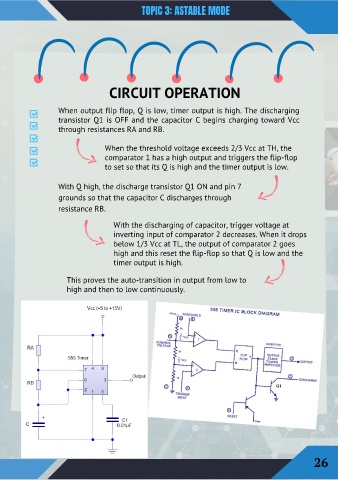

TOPIC 3: ASTABLE MODE

CIRCUIT OPERATION

When output flip flop, Q is low, timer output is high. The discharging

transistor Q1 is OFF and the capacitor C begins charging toward Vcc

through resistances RA and RB.

When the threshold voltage exceeds 2/3 Vcc at TH, the

comparator 1 has a high output and triggers the flip-flop

to set so that its Q is high and the timer output is low.

With Q high, the discharge transistor Q1 ON and pin 7

grounds so that the capacitor C discharges through

resistance RB.

With the discharging of capacitor, trigger voltage at

inverting input of comparator 2 decreases. When it drops

below 1/3 Vcc at TL, the output of comparator 2 goes

high and this reset the flip-flop so that Q is low and the

timer output is high.

This proves the auto-transition in output from low to

high and then to low continuously.

26